## **DESCRIPTION**

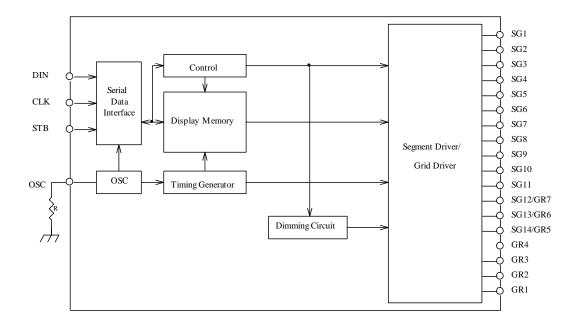

DL8838 is and LED Controller driven on a 1/4 to 1/7 duty factor. Fourteen to eleven segment output lines, 4 to 7 grid output lines, one display memory, control circuit are all incorporated into a single chip to build a highly reliable peripheral device for a single chip microcomputer. Serial data is fed to DL8838 via a three-line serial interface. Housed in a 28-pin SO Package, DL8838's pin assignments and application circuit are optimised for easy PCB Layout and cost saving advantages.

### **FEATURES**

- CMOS technology

- Low power consumption

- 8-step dimming circuitry

- Serial interface for clock, data input, strobe pins

- Available in 28-pin, SO package

### APPLICATION

Microcomputer peripheral device

### **BLOCK DIAGRAM**

Page 1 of 13

## PIN CONFIGURATION

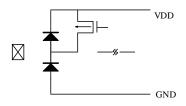

## INPUT/OUTPUT CONFIGURATIONS

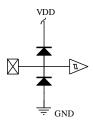

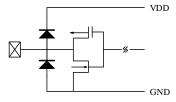

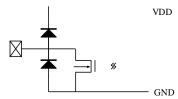

The schematic diagrams of the input and output circuits of the logic section are shown below.

Input Pins: CLK, STB&DIN

Output Pins: SG14/GR5 TO SG12/GR7

Output Pins: GR1 to GR4

Output Pins: SG1 to SG11

Page 2 of 13

### PIN DESCRIPTION

| Pin Name             | I/O | Description                                                            | Pin No. |  |

|----------------------|-----|------------------------------------------------------------------------|---------|--|

| OSC                  | Ι   | Oscillator Input Pin A resistor is connected to this pin to determine  | 1       |  |

| OSC                  | 1   | the oscillation frequency                                              |         |  |

| DIN                  | I   | Data Input Pin This pin inputs serial data at the rising edge of the   | 2       |  |

| DIN                  | 1   | shift clock (starting from the lower bit)                              |         |  |

| CLK                  | I   | Clock Input Pin The pin reads serial data at the rising edge.          | 3       |  |

| STB                  | I   | Serial Interface Strobe Pin The data input after the STB has fallen is | 4       |  |

| 210                  | 1   | processed as a command. When this pin is "HIGH", CLK is ignored.       |         |  |

| VDD                  | 1   | Power Supply                                                           | 5,20    |  |

| SG1 to SG11          | 0   | Segment Output Pins(p-channel, open drain)                             | 6~16    |  |

| SG12/GR7 to SG14/GR5 | О   | Segment Output Pin/Grid Output Pin (CMOS Output )                      | 17~19   |  |

| GND                  | 1   | Ground Pin                                                             | 21,26   |  |

| GR4 to GR1           | О   | Grid Output Pins (n-channel, open drain)                               | 22~25   |  |

| NC                   | -   | No Connection                                                          | 27,28   |  |

### **FUNCTIONAL DESCRIPTION**

#### **Commands**

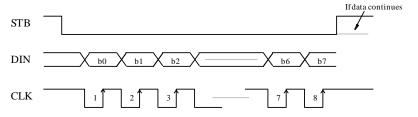

A command is the first byte (b0 to b7) inputted to DL8838 via the DIN Pin after STB Pin has changed from "HIGH" to "LOW" State. If for some reason the STB Pin is set to "HIGH" while data or commands are being transmitted, the serial communication is initialised, and the data/commands being transmitted are considered invalid.

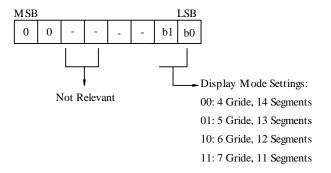

#### COMMAND 1:DISPLAYMODE SETTING COMMANDS

DL8838 provides 4 display mode settings as shown in the diagram below: As stated earlier a command is the first one byte (b0 to b7)transmitted to DL8838 via the DIN Pin when STB is "LOW". However, for these commands, Bit No.3 to Bit No.6 (b2 to b5) are ignored, Bit No.7&Bit No.8 (b6 to b7)are given a value of "0".

The Display Mode Setting Commands determine the number of segments and grids to be used (1/4 to 1/7 duty, 14 to 11 segments). When these commands are executed, the display is forcibly turned off. A display command "ON" must be executed in order to resume display. If the same mode setting is selected, no command execution is take place, therefore, nothing happens.

When Power is turned "ON", the 7-Grid, 11-Segment Mode is selected.

Page 3 of 13

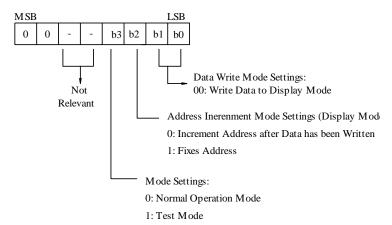

### **COMMAND 2: DATA SETTING COMMANDS**

The Data Setting Commands executes the Data Write Mode for DL8838. The Data Setting Command, the bits 5 and 6 (b4,b5) are ignored, bit 7 (b6) is given the value of "1" while bit 8 (b7) is given the value of "0". Please refer to the diagram below:

When power is turned ON, but 4 to bit 1 (b3 to b0) are given the value of "0".

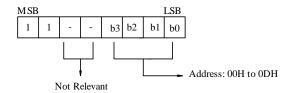

#### **COMMAND 3: ADDRESS SETTING COMMANDS**

Address Setting Commands are used to set the address of the display memory. The address is considered valid if it has a value of "00H to 0DH". If the address is set to 0EH or higher, the data is ignored until a valid address is set. When power is turned ON, the address is set at "00H".

Please refer to the diagram below.

#### Display Mode and RAM Address

Data transmitted from an external device to DL8838 via the serial interface are stored in the Display RAM and are assigned addresses. The RAM Addresses of DL8838 are given below in 8 bits unit.

|      | SG14 | SG13 | SG12 | SG9 | SG8 | SG5             | SG4         | SG1 |

|------|------|------|------|-----|-----|-----------------|-------------|-----|

| DIG1 | HU   | 011  | HL   | 0   | IU  | 00 <sub>F</sub> | $)_{ m HL}$ | 00  |

| DIG2 | HU   | 031  | HL   | 03  | IU  | 02 <sub>F</sub> | $2_{ m HL}$ | 02  |

Page 4 of 13 1/14/2011

| $04_{ m HL}$     | $04_{\mathrm{HU}}$ | $05_{\mathrm{HL}}$          | $05_{\mathrm{HU}}$ | DIG3 |

|------------------|--------------------|-----------------------------|--------------------|------|

| 06 <sub>HL</sub> | 06 <sub>HU</sub>   | $07_{\rm HL}$               | $07_{\mathrm{HU}}$ | DIG4 |

| $08_{ m HL}$     | $08_{\mathrm{HU}}$ | 09 <sub>HL</sub>            | $09_{\mathrm{HU}}$ | DIG5 |

| $0 A_{ m HL}$    | $0 A_{ m HU}$      | $0\mathrm{B}_{\mathrm{HL}}$ | $0B_{ m HU}$       | DIG6 |

| $0C_{HL}$        | $0C_{\mathrm{HU}}$ | $0D_{HL}$                   | $0D_{\mathrm{HU}}$ | DIG7 |

| b0 |         | b3 | b4 |           | b7 |

|----|---------|----|----|-----------|----|

|    | $xxH_L$ |    |    | $xxH_{U}$ |    |

Lower 4 bits Higher 4 bits

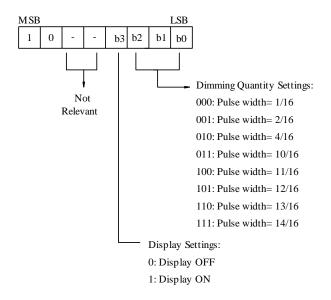

#### **COMMAND 4: DISPLAY CONTROL COMMANDS**

The Display Control Commands are used to turn ON or OFF a display. It also used to set the pulse width. Please refer to the diagram below. When the power is turned ON, a 1/16 pulse width is selected and the displayed is turned OFF

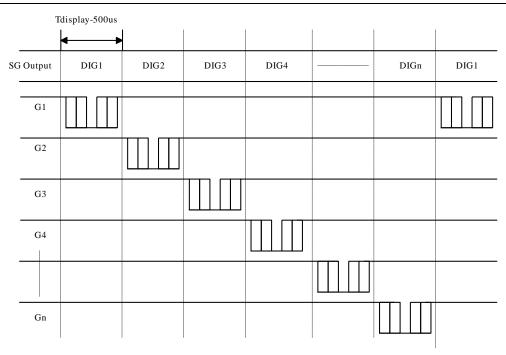

## **DISPLAY TIMING WAVEFORM**

Page 5 of 13

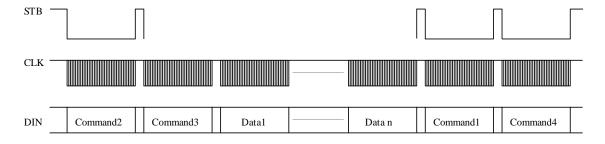

## SERIAL COMMUNICATION FORMAT

The following diagram shows the DL8838 serial communication format

## RECEPTION (Data/ Command Write)

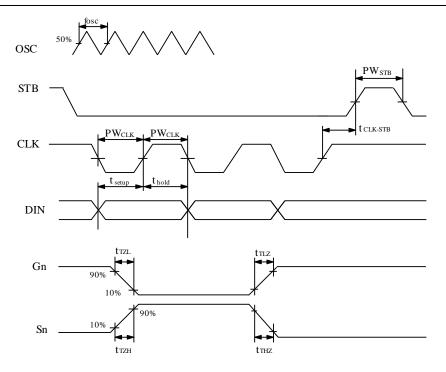

## SWITCHING CHARACTERISTIC WAVEFORM

DL8838 Switching Characteristics Waveform is given below

Page 6 of 13

where:  $PW_{CLK}(Clock\ Pulse\ Width) \geqslant 400nS$   $t_{setup}\ (Data\ Setup\ Time) \geqslant 100nS$   $t_{CLK^-STB}\ (Clock^-Strobe\ Time) \geqslant 1\mu\ s$   $t_{TZH}(Rise\ Time) \leqslant 1\mu\ s$  $t_{TZL} < 1\mu\ s$

$PW_{STB}$  (Strobe Pulse Width)  $\geqslant 1\mu$  s  $t_{hold}$  (Data Hold Time)  $\geqslant 100 nS$   $t_{THZ}$ (Fall Time)  $\leqslant 10\mu$  s fosc= Oscillation Frequency  $t_{TLZ} < 10\mu$  s

## **APPLICATIONS**

Display memory is updated by incrementing addresses. Please refer to the following diagram.

where: Command 1: Display Mode Setting Command

Command 2: Data Setting Command Command 3: Address Setting Command

Page 7 of 13

Data 1 to n: Transfer Display Data (14 Bytes max.)

Command 4: Display Control Command

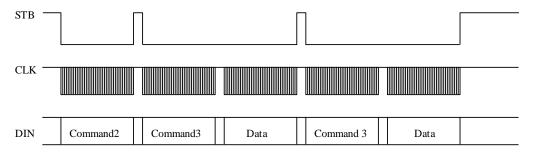

The following diagram shows the waveforms when updating specific addresses.

where:

where: Command 2 — Data Setting Command

Command 3 — Address Setting Command

Data — Display Data

Page 8 of 13 1/14/2011

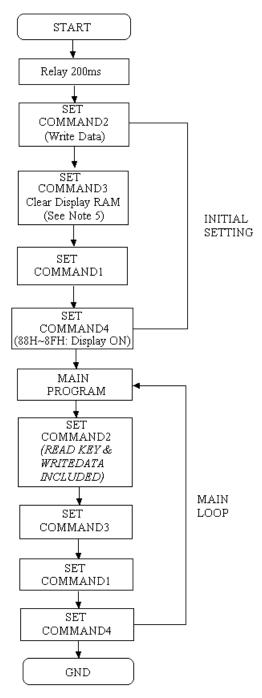

### RECOMMENDED SOFTWARE PROGRAMMING FLOWCHART

Note: 1. Command 1: Display Mode Commands

- 2. Command 2: Data Setting Commands

- 3. Command 3: Address Setting Commands

- 4. Command 4: Display Control Commands

- 5. When IC power is applied for the first time, the contents of the Display RAM is not defined; thus, it is strongly suggested that the contents of the Display RAM must be cleared during the initial setting.

Page 9 of 13

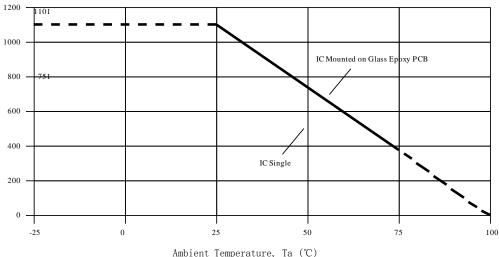

# SOP28 300MIL THERMAL PERFORMANCE IN STILL AIR AT $_{TJ}$ =100 $^{\circ}$ C

Ambient Temperature, Ta (℃)

## ABSOLUTE MAXIMUM RATINGS

(Unless otherwise stated, Ta=25°C, GND=0V)

| Parameter                           | Symbol             | Ratings                      | Unit  |

|-------------------------------------|--------------------|------------------------------|-------|

| Supply Voltage                      | $V_{ m DD}$        | -0.5 to +7.0                 | Volts |

| Logic Input Voltage                 | $V_{\rm I}$        | -0.5 to V <sub>DD</sub> +0.5 | Volts |

| Daives Outsut Comment               | $I_{OLGR}$         | +250                         | mA    |

| Driver Output Current               | $I_{OHSG}$         | -50                          | mA    |

| Maximum Driver Output Current/Total | I <sub>TOTAL</sub> | 400                          | mA    |

## RECOMMENDED OPERATING RANGE

(Unless otherwise stated, Ta=-20 to  $+70^{\circ}$ C, GND=0V)

| Parameter                  | Symbol       | Min.        | Тур. | Max.              | Unit |

|----------------------------|--------------|-------------|------|-------------------|------|

| Logic Supply Voltage       | $V_{ m DD}$  | 4.5         | 5    | 5.5               | V    |

| Dynamic Current (see Note) | $I_{DDdyn}$  | -           | -    | 5                 | mA   |

| High-Level Input Voltage   | $V_{IH}$     | $0.8V_{DD}$ | -    | $V_{\mathrm{DD}}$ | V    |

| Low-Level Input Voltage    | $V_{\rm IL}$ | 0           | -    | $0.3V_{DD}$       | V    |

Note: Test Condition: Set Display Control Commands = 80H (Display Turn OFF State & under no load)

Page 10 of 13 1/14/2011

## **ELECTRICAL CHARACTERISTICS**

(Unless otherwise stated,  $V_{DD}=5V$ , GND=0V, Ta=25 $^{\circ}$ C)

| Parameter                 | Symbol            | Test Condition                      | Min.                        | Typ. | Max.        | Unit |

|---------------------------|-------------------|-------------------------------------|-----------------------------|------|-------------|------|

|                           | ī                 | Vo=V <sub>DD</sub> -1V SG1 to SG11, | 10                          | -14  | -30         | mA   |

| High-Level Output Current | $I_{OHSG(1)}$     | SG12/GR7 to SG14/GR5                | 10                          |      |             | IIIA |

| righ-Level Output Current | ī                 | Vo=V <sub>DD</sub> -2V SG1 to SG11, | -20                         | -25  | -50         | mA   |

|                           | $I_{OHSG(2)}$     | SG12/GR7 to SG14/GR5                | -20                         | -23  | -30         | IIIA |

| Segment High-Level        | ī                 | Vo=V <sub>DD</sub> -1V SG1 to SG11, |                             |      | ±5          | %    |

| Output Current Tolerance  | $I_{TOLSG}$       | SG12/GR7 to SG14/GR5                | -                           | ٦ -  | 70          |      |

| Low Lovel Output Cumont   | T                 | Vo=0.3V GR1 to GR4,                 | 100                         | 140  |             | A    |

| Low-Level Output Current  | $I_{OLGR}$        | SG12/GR7 to SV14/GR5                | 100                         | 140  |             | mA   |

| High-Level Input Voltage  | $V_{\mathrm{IH}}$ | -                                   | $0.8\mathrm{V}_\mathrm{DD}$ | -    | -           | V    |

| Low-Level Input Voltage   | $V_{\mathrm{IL}}$ | -                                   | -                           | -    | $0.3V_{DD}$ | V    |

| Oscillation Frequency     | fosc              | R=51 KOhms                          | 350                         | 500  | 650         | KHz  |

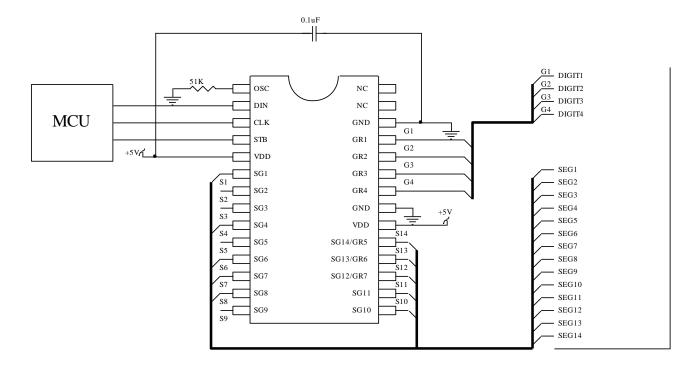

## **APPLICATION CIRCUIT**

Note: 1. The capacitor (0.1uF)connected between be GND and VDD Pins must be located as near as possible to the DL8838 chip.

2. DL8838 power supply is separate form the application system power supply.

Page 11 of 13

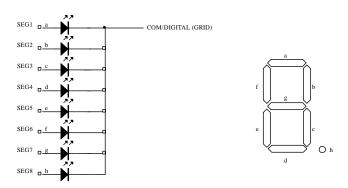

#### COMMON CATHODE TYPE LED PANEL:

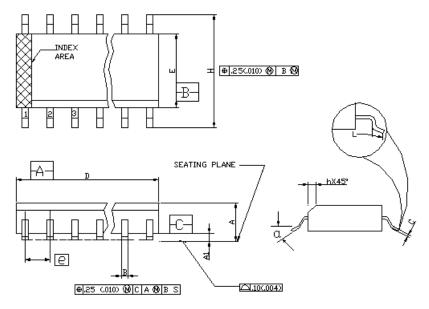

## PACKAGE INFORMATION

28 Pins, SOP Package (300mil)

| Cbl    | D     | Dimensions in Millimeter |       |

|--------|-------|--------------------------|-------|

| Symbol | Min   | Nom.                     | Max   |

| A      | 2.35  |                          | 2.65  |

| A1     | 0.10  |                          | 0.30  |

| В      | 0.33  |                          | 0.51  |

| С      | 0.23  |                          | 0.32  |

| D      | 17.70 |                          | 18.10 |

| Е      | 7.40  |                          | 7.60  |

| e      |       | 1.27 bsc                 |       |

| Н      | 10.00 |                          | 10.65 |

| h      | 0.25  |                          | 0.75  |

| L      | 0.40  |                          | 1.27  |

| α      | 0°    |                          | 8°    |

Page 12 of 13 1/14/2011

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5-1982.

- 2. Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and gate burrs shall not exceed 0.15mm (0.006 in) per side.

- 3. Dimension E does not include interlead flash or protrusions. Interlead flash and protrusion shall not exceed 0.15mm (0.010 in) per side.

- 4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 5. "L" is the length of terminal for soldering to a substrate.

- 6. "N" is the number of terminal positions (N=28).

- 7. The lead width B as measured 0.36mm (0.014in) or greater above the seating plane, shall not exceed a maximum value of 0.61 mm (0.024 in).

- 8. Controlling dimension: MILLIMETER

- 9. Refer to JEDEC MS-013 Variation AE.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

Page 13 of 13